Auto Optical BGA Rework Station

Mye brukt i chip-nivå reparasjon for hovedkort av mobil, bærbar PC, datamaskin, TV, klimaanlegg etc. Den har høy vellykket reparasjonsrate og høy grad av automatisering og sparer mye menneskelig innsats. Vi er en profesjonell produsent av denne maskinen og har denne maskinen tilgjengelig på lager.

Beskrivelse

Auto Optical BGA Rework Station

1. Anvendelse av Auto Optical BGA Rework Station

Hovedkort til datamaskin, smarttelefon, bærbar PC, MacBook logikkkort, digitalkamera, klimaanlegg, TV og annen elektronisk

utstyr fra medisinsk industri, kommunikasjonsindustri, bilindustri, etc.

Egnet for forskjellige typer brikker: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED-brikke.

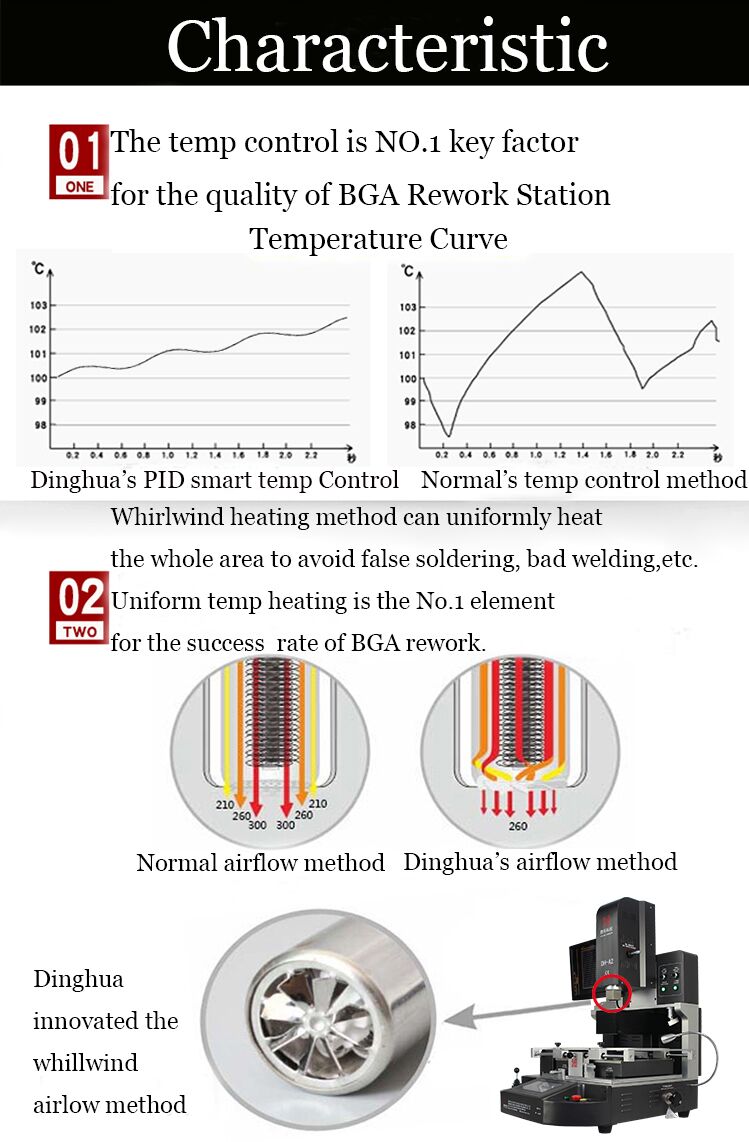

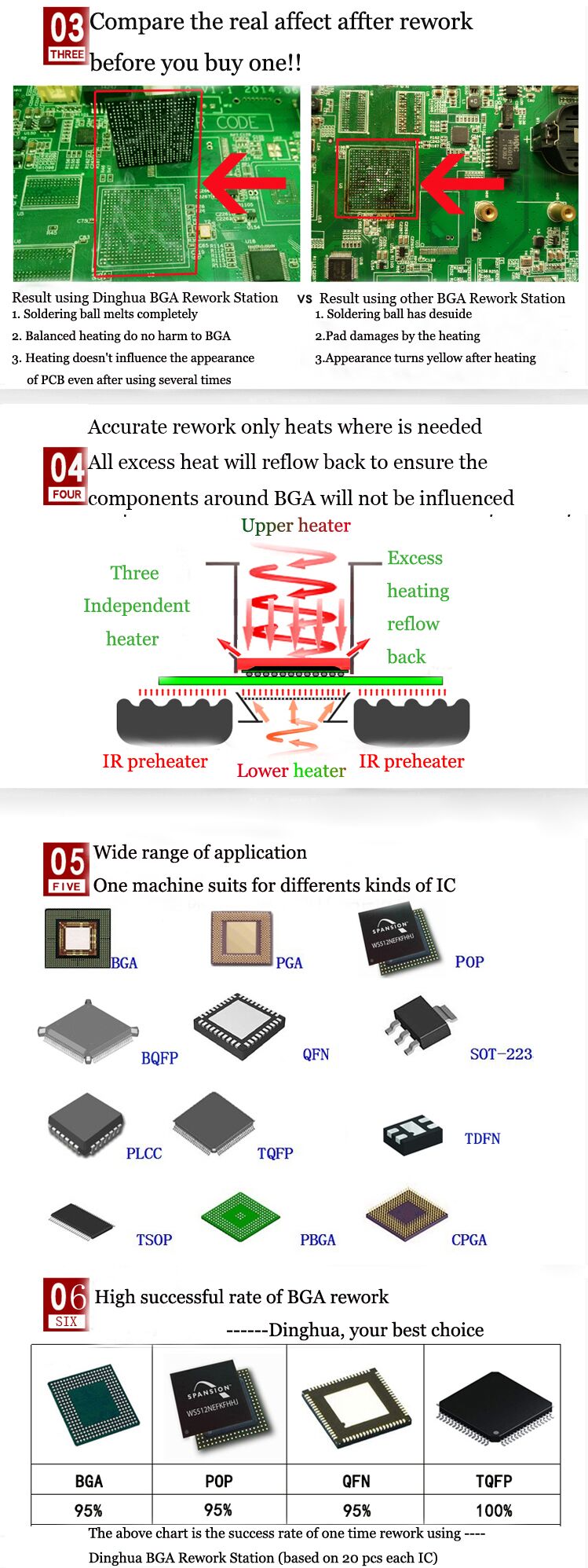

2. Produktfunksjoner til Auto Optical BGA Rework Station

•Høy vellykket reparasjon på brikkenivå. Avlodding, montering og loddeprosessen er automatisk.

• Nøyaktig justering av hver loddeskjøt kan garanteres med optisk justering CCD-kamera.

•Nøyaktig temperaturkontroll kan sikres med 3 uavhengige varmeområder. Maskinen kan stille inn og lagre

1 million temperaturprofil.

• Innebygget vakuum i monteringshodet plukker opp BGA-brikken automatisk etter at loddingen er fullført.

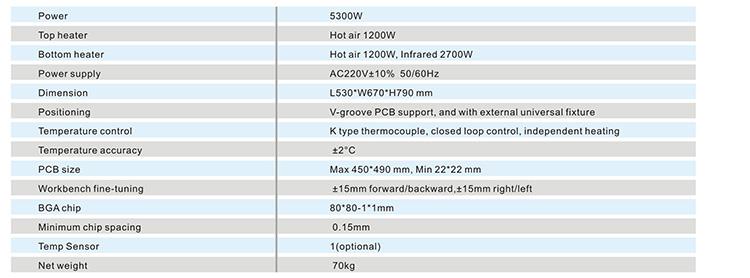

3.Spesifikasjon av Auto Optical BGA Rework Station

4.Detaljer om Auto Optical BGA Rework Station

CCD-kamera (nøyaktig optisk justeringssystem); 2.HD digital skjerm; 3. Mikrometer (juster vinkelen på brikken);

4.3 uavhengige varmeovner (varmluft og infrarød); 5. Laserposisjonering; 6. HD-berøringsskjermgrensesnitt, PLC-kontroll;

7. Led hodelykt ; 8.Joystick-kontroll .

5.Hvorfor velge vår autooptiske BGA Rework Station?

6. Sertifikat for Auto Optical BGA Rework Station

7. Pakking og forsendelse av Auto Optical BGA Rework Station

8.Vanlige spørsmål

Hvordan teste brikken?

Innledende chiptest på systemnivå

SoC er basert på dype submikron-prosesser, så testing av nye Soc-enheter krever en helt ny tilnærming. Fordi hver funksjonell komponent

har egne testkrav, må designingeniøren lage en testplan tidlig i prosjekteringsprosessen.

Blokk-for-blokk-testplanen for SoC-enheter må implementeres: riktig konfigurerte ATPG-verktøy for logikktesting; korte testtider; ny høyhastighet

feilmodeller og flere minne eller små array-tester. For produksjonslinjen finner den diagnostiske metoden ikke bare feilen, men skiller også

feil node fra arbeidsnoden. I tillegg bør testmultipleksingsteknikker brukes når det er mulig for å spare testtid. Innenfor høyt

integrert IC-testing, ATPG og IDDQs testbare designteknikker har en kraftig feilseparasjonsmekanisme.

Andre faktiske parametere som må planlegges på forhånd inkluderer antall pinner som må skannes og mengden minne ved hver pinneende.

Grenseskanninger kan bygges inn i SoC, men er ikke begrenset til sammenkoblingstester på kort eller multi-chip-moduler.

Selv om brikkestørrelsen minker, kan en brikke fortsatt pakke millioner til 100 millioner transistorer, og antallet testmoduser har økt til enestående

nivåer, noe som resulterer i lengre testsykluser. Dette problemet kan testes. Modus komprimering for å løse, kan kompresjonsforholdet nå 20 prosent til 60 prosent. For dagens storskala

brikkedesign, for å unngå kapasitetsproblemer, er det nødvendig å finne testprogramvare som kan kjøres på 64-bit-operativsystemer.

I tillegg står testprogramvare overfor nye testproblemer forårsaket av dype sub-mikron prosesser og økende frekvens. I det siste, ATPG testmodus for

testing av statiske blokkeringsfeil var ikke lenger aktuelt. Å legge til funksjonelle mønstre til tradisjonelle verktøy gjorde det vanskelig å finne nye feil. En bedre tilnærming er å

klassifiser tidligere funksjonsmodusgrupper for å finne ut hvilke feil som ikke kan oppdages, og lag deretter en ATPG-modus for å fange opp disse manglende feiltypene.

Etter hvert som designkapasiteten øker og testtiden per transistor reduseres, for å finne hastighetsrelaterte problemer og verifisere krets timing, en synkron testmetode

må være ansatt. Synkron testing må inkludere flere feilmodeller, inkludert transientmodeller, baneforsinkelser og IDDQ.

Noen selskaper i bransjen mener at det å kombinere blokkerings-, funksjons- og forbigående/baneforsinkelsesfeil kan være den mest effektive teststrategien. For dypt

submikronbrikker og høyfrekvent drift, transient- og baneforsinkelsestesting er enda viktigere.

For å løse problemet med ATE-nøyaktighet ved synkronisering av testkjernen og redusere kostnadene, er det nødvendig å finne en ny metode som forenkler grensesnittet til

testenheten (transient- og baneforsinkelsestest krever nøyaktig klokke ved testenhetens grensesnitt), Den sikrer at signalet er nøyaktig nok under testen.

Siden det er stor mulighet for produksjonsfeil i SoC-minneblokken, må minnet BIST ha en diagnostisk funksjon. Når et problem er funnet,

den defekte adresseenheten kan tilordnes det redundante minnet til reserveadresseenheten, og den oppdagede feiladressen vil bli forkastet. Unngå å kaste

hele den dyre brikken.

Testing av små innebygde minneblokker eliminerer behovet for ytterligere porter eller kontrolllogikk. For eksempel kan testteknikker for vektorkonvertering konvertere

funksjonelle moduser til en rekke skannemoduser.

I motsetning til BIST-metoden, krever ikke den funksjonelle inngangen til bypass-minneblokken ytterligere logikk. Fordi ingen ekstra testlogikk er nødvendig, vil SoC

utviklingsingeniører kan gjenbruke testmønstre som ble dannet tidligere.

Avanserte ATPG-verktøy tester ikke bare makroer parallelt, men bestemmer også om det er konflikter, samt detaljer om hvilke makroer som kan testes parallelt og hvilke

makroer kan ikke testes parallelt. I tillegg kan disse makroene testes effektivt selv om makroklokken er den samme som skanneklokken (som f.eks. synkront minne).

For tiden er det ikke nok testpunkter på det tette dobbeltsidige kortet, og hver kompleks brikke må være utstyrt med en grenseskanningskrets. Uten

grenseskanninger, produksjonsfeiloppslag på tavlenivå er ganske vanskelige og kan ikke engang bli funnet. Med grenseskanning er testing på tavlenivå ekstremt enkelt

og uavhengig av de logiske kretsene i brikken. Grenseskanning kan også konfigurere ATPG-modusen til skannekjeden til brikken på et hvilket som helst stadium av produksjonen.